Etron Unveils Cutting-edge Innovations as

CES Innovation Award Honoree at CES 2024

Come and visit our CES ’24 booth to experience the demos and chat with our in-house experts!

KGDM™

Known Good Die Memory

A Pioneer and Leader in KGD Memory

- Enable the Integration of Memory and System-Chip in One Package

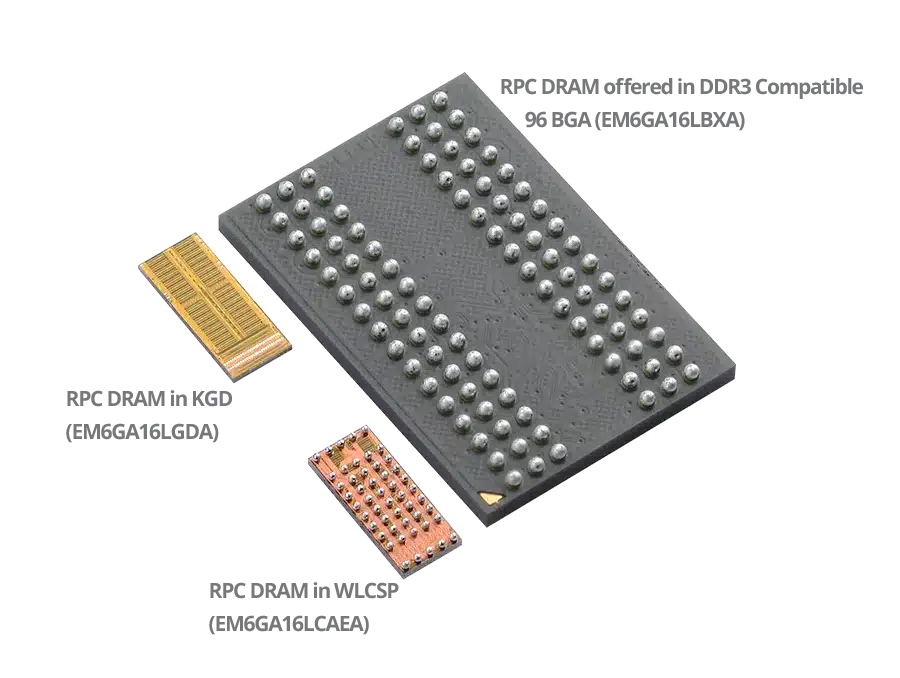

RPC DRAM®

Low Pin Count DRAM

World′s 1st DRAM in Wafer Level Chip Size Package (WLCSP)

- The Smallest and Least Expensive Package Option

LRTDRAM™

Long Retention Time DRAM

- Significantly Extend the Retention Time through DRAM Circuit Design

- Best for the High-Temperature Applications

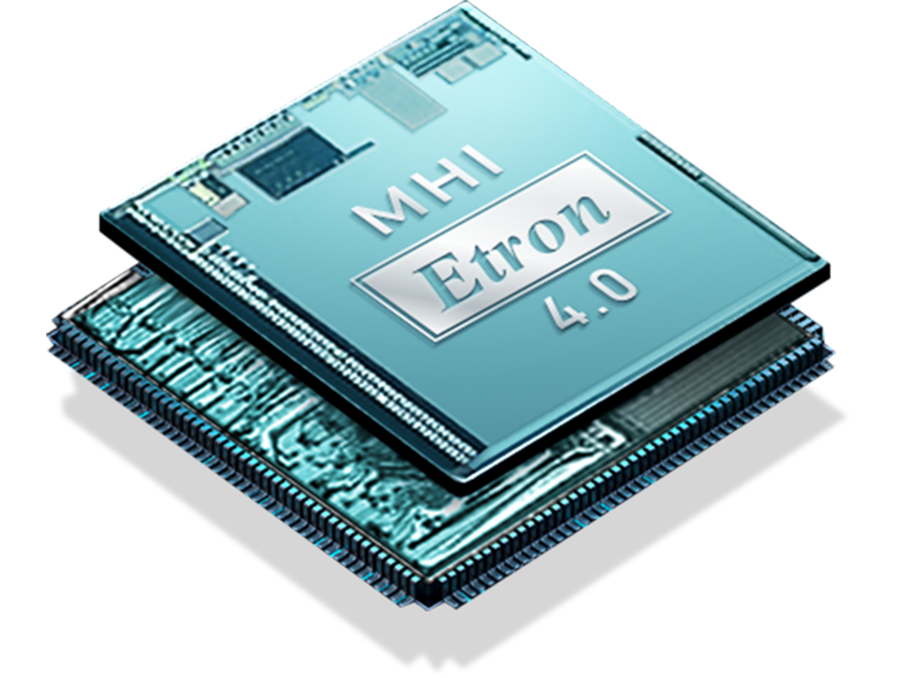

Monolithic and Heterogeneous Integration (MHI™)

- Optimizing MHI of Si & Non-Si Materials/Devices

- Creating Self-Smart MicroSystems

SUSTAINABILITY

ESG

Etron Technology, Inc. management team recognizes that compliance with the Responsible Business Alliance (RBA) Code of Conduct is the basic condition for a responsible company and the dedication of its efforts. Besides profitability, the company should pursue the principle of “Utilize whatever you take from the society and contribute back to the society”, and extend the influence over stakeholders, including employees, customers, suppliers, shareholders, the public and the government to meet their expectations.

NEWS

Latest News-

Product News

DeCloakVision, a trustable multimodal AI privacy-enhanced surveillance system, distinguishes itself in the field of artificial intelligence, receiving 2024 CES Innovation Award.

-

Revenues

Etron Announces Revenue of November 2023

-

Technical Papers

What is KGD? Understanding the definition, functions, and application examples of KGD.

-

Video/Event

Etron@CES 2024: The Future of AI-Powered Intelligence, Connectivity, Autonomy & Confidentiality

RECRUIT

Join UsEtron supports our colleagues with competitive career development and life-enhancing programs. Besides professional courses taught by company instructors or invited speakers, we encourage employees to participate in external occupational training programs

- Initiative

- Honor

- Courage

- Team

COMPANY

About EtronEtron Technology, Inc. (Taiwan GTSM: 5351) is a world-class fabless IC design and product company founded in February 1991, specializing in buffer memory and system-on-chips.